## ADAG GATEME

| USN   |                | 17ELN15/2                                                                                                                                                                                         |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Fir            | st/Second Semester B.E. Degree Examination, Dec.2018/Jan.2019                                                                                                                                     |

|       |                | Basic Electronics                                                                                                                                                                                 |

| Tin   | 1 <b>0</b> • 1 | hrs. Max. Marks: 10                                                                                                                                                                               |

| 1 111 | 10             | Note: Answer any FIVE full questions, choosing                                                                                                                                                    |

|       |                | ONE full question from each module.                                                                                                                                                               |

|       |                | Module-1                                                                                                                                                                                          |

| 1     | a.             | Explain the operation of PN junction diode under forward and reverse bias condition.                                                                                                              |

|       |                | (07 Mark                                                                                                                                                                                          |

|       | b.             | Discuss the load and line regulations using zener diode with neat circuit diagrams at                                                                                                             |

|       | c.             | appropriate expressions. (08 Mark<br>Design a 9V DC reference source consisting of a zener diode and series connected resistor                                                                    |

|       | С.             | operate from a 24V supply. $[I_{ZT} = I_Z = 20 \text{ mA}]$ . (05 Mark                                                                                                                            |

|       |                | operate from a 217 suppry. [12] 12 25 in 4.                                                                                                                                                       |

|       |                | ØR .                                                                                                                                                                                              |

| 2     | a.             | With a neat circuit diagram, explain the operation of centre tapped full wave rectifier. Dra                                                                                                      |

|       |                | input and output waveforms. (07 Mark                                                                                                                                                              |

|       | b.             | Draw common emitter circuit, sketch input and output characteristics and explain thr                                                                                                              |

|       |                | regions of operation. (08 Mark                                                                                                                                                                    |

|       | c.             | Derive the relationship between $\alpha$ and $\beta$ . Find $I_C$ and $I_E$ for the transistor with $\alpha=0.99$ at                                                                              |

|       |                | $I_B = 20\mu A$ . (05 Mark                                                                                                                                                                        |

|       |                |                                                                                                                                                                                                   |

|       |                | Module-2                                                                                                                                                                                          |

| 3     | a.             | Precisely analyse the circuit of voltage divider bias. (08 Mark What is Op-Amp? List out the ideal and particle characteristics of Op-Amp. (07 Mark)                                              |

|       | b.<br>c.       | What is Op-Amp? List out the ideal and particle characteristics of Op-Amp. (07 Mark Calculate the output voltage of a summer. Given: $R_1 = 200k\Omega$ , $R_2 = 250k\Omega$ , $R_3 = 500k\Omega$ |

|       | ٥.             | $R_f = 1M\Omega$ , $V_1 = -2V$ , $V_2 = -1V$ and $V_3 = +3V$ . (05 Mark                                                                                                                           |

|       |                | (05 Maris                                                                                                                                                                                         |

|       |                | OR                                                                                                                                                                                                |

| 4     | a.             | Design a base bias circuit to have $V_{CE} = 5V I_C = 5mA$ . The supply voltage is 15V and                                                                                                        |

|       |                | transistor has $h_{fe} = 100$ . (07 Mark                                                                                                                                                          |

|       | b.             | Derive an expression for the voltage gain of inverting and Non-inverting amplifier.                                                                                                               |

|       |                | (08 Mark                                                                                                                                                                                          |

|       | C.             | Analyse the circuit of an op-amp as an integrator. (05 Mark                                                                                                                                       |

|       |                | Module 2                                                                                                                                                                                          |

| 5     | a.             | Interpret the following:  Module-3                                                                                                                                                                |

| J     | u.             | i) $(48350)_{10} = ()_{16} = ()_{8}$                                                                                                                                                              |

|       |                | ii) $(FACE)_{16} = (\ \ \ \ \ )_2 \stackrel{?}{=} (\ \ \ )_8$                                                                                                                                     |

(06 Marks)

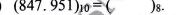

iii) (847. 951)<sub>10</sub> = ( )<sub>8</sub>.

b. Write the logical symbol, truth table and Boolean expressions of all the logic gates : (AND, OR, NOT, NOR, NAND, EX-OR, EX-NOR).

c. Realize EX -OR gate using NAND gates only. (09 Marks)

(05 Marks)

|     |    | OR OR                                                                                |               |

|-----|----|--------------------------------------------------------------------------------------|---------------|

|     |    | Which are the universal gates? Realize basic gates using universal gates?            | (07 Marks)    |

| 6   | a. | Design a full adder using two half adder. Derive the necessary expressions.          | (08 Marks)    |

|     | b. | Perform the subtraction using 2's complement method:                                 |               |

|     | c. | i) $(11010)_2 - (10000)_2$                                                           |               |

|     |    | ii) $(11)_{10} - (15)_{10}$ .                                                        | (05 Marks)    |

|     |    | 11) (11)10 (13)10.                                                                   |               |

|     |    |                                                                                      |               |

|     |    | Module-4                                                                             |               |

| 7   | a. | With diagram and truth table explain NAND gate latch.                                | (06 Marks)    |

|     | b. | Explain the operation of 8051 microcontroller with neat block diagram. Mention       | n the salient |

|     |    | features                                                                             | (10 Marks)    |

|     | c. | Distinguish between flip-flop and latch. List out the applications of flip-flop.     | (04 Marks)    |

|     |    |                                                                                      |               |

|     |    |                                                                                      |               |

|     |    | OR                                                                                   | (07 Mandas)   |

| 8   | a. | Explain the operation of clocked RS flip-flop.                                       | (07 Marks)    |

|     | b. | With a neat block diagram, explain microcontroller based stepper motor control s     | (07 Marks)    |

|     |    | The standard NOP Cote Letch                                                          | (06 Marks)    |

|     | C. | With a diagram and truth table, explain NOR Gate Latch.                              | (00 1/14/145) |

|     |    |                                                                                      |               |

|     |    | Module-5                                                                             |               |

| 0   |    | What is modulation? Explain the need for modulation.                                 | (04 Marks)    |

| 9   | a. | Derive the expression for frequency modulation with a neat waveforms.                | (10 Marks)    |

|     | b. | Explain the piezoelectric and photo electric transducers.                            | (06 Marks)    |

|     | C. | Explain the piezoelectric and photo electric transactors.                            |               |

|     |    |                                                                                      |               |

|     |    | OR                                                                                   |               |

| -10 | a. | Discuss the comparison between AM and FM modulation.                                 | (06 Marks)    |

| 10  | b. | Explain the construction and principle of operation of LVDT.                         | (07 Marks)    |

|     | c. | A carrier of 1MHz with 400 Watt of its power is amplitude modulated with             | a sinusoidal  |

|     | •  | signal of 2500 Hz. The depth of modulation 75%. Calculate the side band free         | quencies, the |

|     |    | band width, the power in the side bands and the total power in the modulated wa      | ve.           |

|     | P  |                                                                                      | (07 Marks)    |

|     |    |                                                                                      |               |

|     |    |                                                                                      |               |

|     |    | ****                                                                                 |               |

|     |    |                                                                                      |               |

|     |    |                                                                                      |               |

|     |    |                                                                                      |               |

|     |    |                                                                                      |               |

|     |    |                                                                                      | •             |

|     |    |                                                                                      |               |

|     |    |                                                                                      |               |

|     |    | sgargal wit state 💙 may gree and autobate at the final flooring blooger, e.t. eleter |               |

|     |    | 2 of 2                                                                               |               |

|     |    | 2 of 2                                                                               |               |

|     |    | Co                                                                                   |               |

|     |    |                                                                                      |               |

|     |    | A P                                                                                  |               |

|     |    |                                                                                      |               |

|     | 1  |                                                                                      |               |

|     |    |                                                                                      |               |